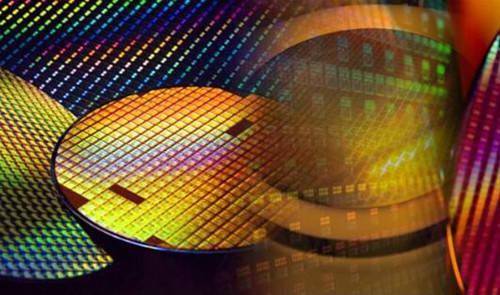

原标题:台积电 3nm 制程工艺计划今日量产

12 月 29 日消息,台积电今天将在台南科学园区举办 3 纳米量产暨扩厂典礼,正式宣布启动 3 纳米大规模生产。

新年伊始,台积电将采用产能有限的 N3 节点工艺,然后在 2023 年晚些时候转向更稳定、更高效的全面生产的 N3E,随后在 2024 年转向 N3P,这一年台积电还将在新竹工厂将其 2 纳米 GAA 工艺投入试生产,并在 2025 年进行大规模生产。

在此前多个季度的财报分析师电话会议上,台积电 CEO 魏哲家曾表示,他们在按计划推进 3nm 制程工艺以可观的良品率在下半年量产,在高性能计算和智能手机应用的推动下,预计产量在 2023 年将平稳提升。

台积电在官网公布的信息显示,他们的 3nm 制程工艺,是 5nm 之后的另一个全世代制程,具备最佳的 PPA 及电晶体技术。同 5nm 制程工艺相比,3nm 制程工艺的逻辑密度将增加约 70%,在相同功耗下速度提升 10-15%,或者在相同速度下功耗降低 25-30%。

IT之家了解到,三星于 6 月开始制造 3 纳米半导体,并准备在 2024 年推出更节能的 3 纳米节点。该公司的芯片将被用于 Nvidia 显卡、高通移动处理器、IBM CPU 和百度云服务器芯片。目前,三星在全球半导体市场份额方面远远落后于台积电,位居第二。